# 圓

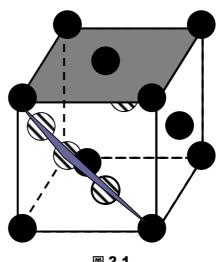

般而言物質以我們所熟悉的三態:氣態、液態與固態的狀態存在, 而固態主要又可區分爲結晶態 (crystalline) 與非結晶態 (amorphous)。一般的金屬 (metals) 與陶瓷 (ceramics) 材料在固態時都屬於結 晶態,而我們日常所熟悉的玻璃是非結晶態的陶瓷材料。結晶態的固體 — 一 晶體 (crystals) 在微觀上,具有三度空間重複性的長距規律性 (longrange order)。也就是說以原子的尺寸觀之,晶體是由一小的晶胞 (unit cell) 在空間中規律的重複建構而成。以**鋁金屬 (aluminum)** 爲例,在一般情形 下它是以面心立方 (face-centered cubic, FCC) 的結構存在。也就如圖 2.1 所示,鋁原子是依 FCC 的組成單元,在三度的空間中重複的排列成了結晶 的鋁金屬。

圖 2.1

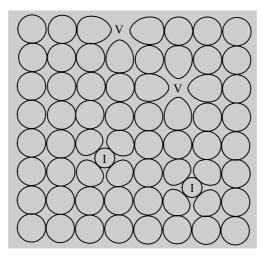

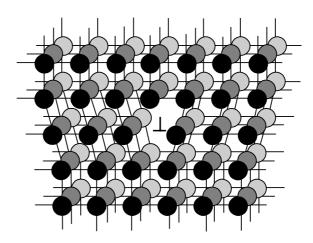

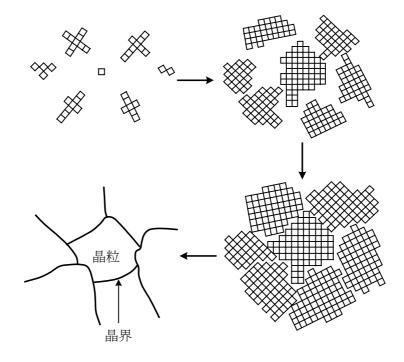

然而在真正的晶體中,通常都含有一些缺陷 (defects)。這些晶體的缺陷包含了點缺陷 (point defects),如在晶體當中的某個原子不見了,即所謂的空洞 (vacancy),如圖 2.2 所示。原子的自然跳動,就可能產生空洞,所以一般而言空洞的缺陷是必然存在,不能完全消除的。晶體的缺陷亦包含了線的缺陷 (line defects),如圖 2.3 所示的刃狀差排 (edge dislocation),由圖中可以見到所多出的一個平面。材料是否爲單晶 (single crystal) 或是一般晶體,則是由是否存在著面缺陷中的晶界 (grain boundary) 來區分,如圖 2.4 所示,而由每個晶界所包圍起來的部份則爲一個晶粒 (grain)。晶界的產生原因甚多,機構之一爲如圖 2.4 所示,當物質由液態轉變成結晶

V:Vacancy I:Interstitial

圖 2.2

圖 2.3

圖 2.4

態時,若是晶核 (nucleus) 超過一處,則每個穩定的晶核將依著各自的方向成長,當這些不同的晶粒成長至碰到一起時,在其邊界就會因成長方向的不同,產生了晶界的缺陷。如果在整個材料中,沒有存在任何晶界,即整個材料是由單一個晶粒所構成,這樣的材料稱爲單晶材料。

在一般的積體電路製造中,基於電性的需求,大多使用單晶的基材,而且是以矽的基材為主。除了矽基材外,III-V 族與 II-IV 族的化合物半導體 (compound semiconductor),如砷化鎵 (GaAs),在高頻的應用上也有一些市場,但在目前都難以與矽的使用量相提並論。矽晶圓 (silicon wafer)就是單晶矽的薄片,爲積體電路製作的基材。如果以種田爲例,矽晶圓就是那積體電路製造業中用以耕種的稻田。以作畫爲例,矽晶圓則是那空白的畫布。矽是地球上蘊藏量第二豐盛的元素,佔了地表的 20%,主要是以氧化矽 (silica, SiO<sub>2</sub>)或其它矽氧化合物 (silicates)的型態存在。

矽晶圓生產的第一步驟,就是將自然界中的矽砂 (SiO<sub>2</sub>),於電爐中藉 由與焦碳的反應還原爲矽。由這製程所得到的矽,其純度較低,而且也不 是單晶,一般稱爲冶金級的矽 (metallurgical-grade silicon)。將冶金級的矽

### 12 電子構裝技術與材料

與無水的氯化氫 (HCl),於高溫如  $800^{\circ}$ C 中反應,則生成四氯化矽 (silicon tetrachloride, SiCl<sub>4</sub>) 與矽烷的氯化物,SiHCl<sub>3</sub>。這些含矽的化合物,如 SiHCl<sub>3</sub> 與矽烷 (silane, SiH<sub>4</sub>) 等,將進一步藉由蒸餾等方法純化,然後 還原成矽,以得到高純度的半導體級矽 (semiconductor-grade silicon)。半 導體級矽的純度雖高,但還不是單晶的矽。

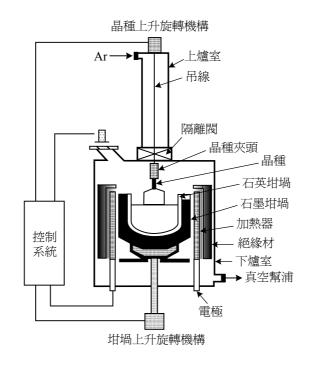

單晶矽生產的最常見方法,是利用從熔融的純矽中,以拉晶 (crystal pulling) 的手段來製造單晶的晶棒 (ingot),這樣的方法稱爲柴氏長晶法 (czochralski method)。如圖 2.5 所示,半導體級的純矽首先於坩堝中加熱熔融。若是組成中必需有其它添加物,如砷元素等,也一併熔融混合成爲均匀的溶液。有著一定晶面 (crystal plane) 的矽晶種 (seed) 緩緩降下,接觸到融湯的液面。藉由液面溫度的精確控制於矽的熔點附近,可開始在晶種接觸點生成結晶。拉晶棒再緩緩往上拉升,若控制良好可長成一定需求尺寸的晶棒。而此結晶的成長之晶面,是由其所用的晶種來控制。以柴氏拉晶法所得的單晶晶棒,直徑大小總是有些變化起伏。而且因偏析 (segregation) 與含氧量分佈等原因,晶棒的電氣性質從外到內並不完全均一。

圖 2.5

因此,此單晶晶棒需進一步將圓週拋光切齊,再將圓週拋光的晶棒切片。 此單晶矽薄片尚需進行研磨與拋光及必要的表面處理,就完成了矽晶圓的 製作。

如圖 2.5 所示,一個典型的柴氏長晶爐包括了爐體、拉升機構、氣氛控制及偵測控制系統等四個主要部份。為了避免矽於高溫下產生劇烈的氧化,長晶一般皆在半密閉的爐體中於氫氣的氣氛下進行。爐體通常區分為上爐室與下爐室,下爐室是主要的加熱區,純度非常高的多晶矽於下爐室的石英坩堝中熔融。石英坩堝因為直接與矽融湯直接接觸,所以在純度與品質的控制上非常重要,不純的石英將引起最終矽晶圓產品的品質下降。石英坩堝會與矽融湯反應,將矽晶圓中氧含量提高,雖然太多的氧會引起許多電性與機械性質的不良效應。適當的氧含量會提升矽晶圓的機械強度,對矽晶圓的品質反而是有利的。矽與石英的反應會產生氣態的 SiO 離開融湯,爐體內的壓力通常保持在 5~100 torr 之間。壓力太低可能會引起融湯沸騰,太高的壓力又可能產生 SiO 凝結掉入矽融湯表面,引起長晶之各種缺陷。

純矽的導電度(conductivity)在  $20^{\circ}$ C 時爲  $5\times10^{-4}\Omega^{-1}\cdot m^{-1}$ ,其能隙 (energy gap) 爲 1.1 eV,屬於半導體(semiconductor)。一般而言半導體的 導電度在  $10^{-6}\Omega^{-1}\cdot m^{-1}$  到  $10^{4}\Omega^{-1}\cdot m^{-1}$  間,而金屬導體(conductor)的導電 度則在  $10^{7}\Omega^{-1}\cdot m^{-1}$  左右。能隙是指原子中其價電帶(valence band)與導電帶(conduction band)的能量差,代表的是電子從價電帶跳到導電帶成爲自由電子所需的能量,一般的絕緣體(insulator)的能隙常在 7 eV 以上。 半導體可區分爲元素型半導體(elemental semiconductor)與化合物型半導體(compound semiconductor),矽與鍺屬前者,後者則包括了 III-V 族的 GaAs 與 II-VI 族的 ZnSe 等。

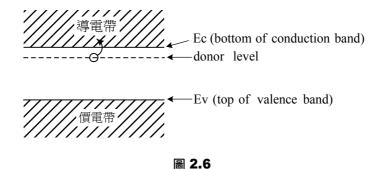

純矽不含雜質因此又屬於本質半導體 (intrinsic semiconductor),在本質半導體中的電氣性質均來自其本身材料的特性。而外質半導體 (extrinsic semiconductor) 則與其不同,在外質半導體中因半導體中掺入了雜質,外質半導體的電氣性質則主要受到掺雜物 (dopant) 的影響。以純矽爲例,如果在純矽中掺入磷,因矽在價電帶原有四個電子,但磷在價電帶卻有五個電子。此多出價電帶所能接受八個電子的多餘電子,被擠出位於較高的電

### 14 電子構裝技術與材料

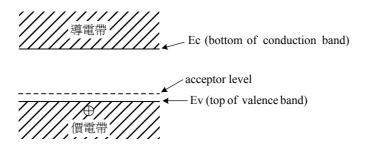

子能階,稱爲**施體能階** (donor level),如圖 2.6 所示。此多出的電子也因此 很容易跳到導電帶成爲自由電子,這樣的半導體稱爲 n- 型半導體。如果純 矽中摻雜的是三價的鋁,則在鋁矽的鍵結中少了一個價電子,因此很容易從 週遭抓進一個電子。這接受電子的能階將遠低於導電帶的能階,如圖 2.7 所 示,稱爲**受體能階** (acceptor level)。這樣的外質半導體將產生**電**洞 (electron hole) 的移動,稱爲 p- 型半導體。在矽晶圓的生產上有純矽的矽晶圓,亦有已含一定摻雜物的 n- 型或 p- 型矽晶圓。其摻雜的濃度隨不同的電性要求而有所改變,一般而言約在 10<sup>14</sup> 到 10<sup>19</sup> atom/cm³ 之間。

縱使在摻雜量被認爲很大的重度摻雜,如高到  $10^{20}$  atom/cm³,其相對的量與矽比較還是十分小量的。爲了製程上控制的容易,摻雜物的添加通常是以母合金 (master alloy) 的形式來添加,而不是以純元素的形式添加。在有摻雜物添加的矽融湯中,在其長晶的過程中,偏析 (segregation) 是無可避免的情形。長晶過程中,拉升機構的旋轉可以減低區域性的偏析,但仍不能避免晶棒頭端與尾端成份的差異。這種偏析是因材料在液態

圖 2.7

與固態中對摻雜物所具有不同的溶解度而來,是材料的本質特性之一,無 可避免,但可以由理論推之偏析的情形。於晶棒長成後,將頭尾端超出組 成規範的部份切除。

在矽晶圓中另一項特徵是晶面,晶面的標示是以**米勒**指標(miller index)表示。以如圖 2.1 所示的 FCC 爲例,依其組成單元可以定義出原點與互相垂直 X, Y, Z 三軸。而晶面與此三軸交點截距的倒數,即爲此晶面的米勒指標。如圖 2.1 中標示斜線的二個晶面,與此三軸交點截距分別是  $(\infty,\infty,1)$  及 (1,1,1),所以這二個晶面分別是 (0,0,1) 及 (1,1,1) 晶面。在 (0,0,1) 面上,面積爲  $a^2$  之內共有  $(1+4\times1/4)=2$  個原子。而在 (1,1,1) 面中,於  $\frac{\sqrt{3}}{2}a^2$  的面積中亦有  $(3\times1/2+3\times1/6)=2$  個原子。可見二個晶面的堆積密度並不相同,由此可見對同樣物質的晶體,不同的晶面其性質並不完全一樣。在一般的多晶物質中因有非常多的晶粒與各種不同的晶面,所表現出來的是各晶面平均的性質,因此一般多晶的材料並不特別注意晶面的方向。然而在單晶材料的使用上,如前所述不同的晶面具有不同的性質,因此晶面的選擇十分重要。在長晶的過程中,在矽晶棒中可以見到很獨特的晶線,這些晶線的存在是由於晶體各面的成長速率不同所引起的。矽的結構是**鑽石結構**(diamond structure),其結構宛如二個套在一起的 FCC,p- 型 <100> 的矽晶圓是最常使用的晶圓。

- **1.** W. R. Runyan and K. E. Bean, "Semiconductor Integrated Circuit Processing Technology", Addison-Wesley, Reading, Massachusetts, 1994.

- **2.** W. R. Runyan, "Silicon Semiconductor Technology", McGraw-Hill, New York, 1974.

- **3.** L. H. Van Vlack, "Elements of Materials Science and Engineering", 6th ed., Addison-Wesley, Reading, Massachusetts, 1990.

- 4. 林明獻, 矽晶圓半導體材料技術, 全華科技圖書, 1999。

### 16 電子構裝技術與材料

# 本章習題

- 1. 什麼是晶界?

- 2. 簡述柴氏長晶法之製程。

- 3. 在一片8吋的矽晶圓中,約有多少個矽原子?

- 4. 一根8吋的矽晶棒,若長一公尺,約有多重?

- **5.** 何謂偏析?